"Como assim por que teve de ser criado? É um bypass (atalho). Você precisa criar bypasses." (Douglas Adams; O Guia do Mochileiro das Galáxias, 1979).

# Construindo Forwardings (Bypasses)

Paulo Ricardo Lisboa de Almeida

### Hazards de Dados

O pipeline construído até o momento funciona caso as instruções não tenham dependências.

Mas hazards de dados e de controle são comuns.

Hazards estruturais já foram resolvidos.

Vamos tratar hazards de dados via **Forwardings**.

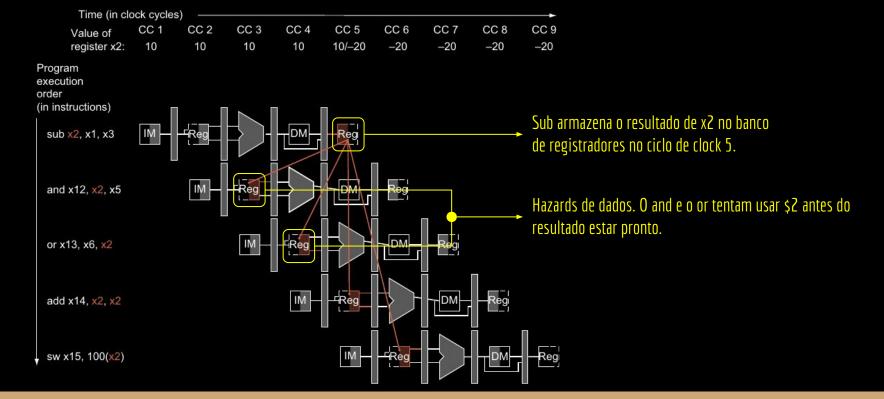

Considere as instruções a seguir

```

sub x2,x1,x3

and x12,x2,x5

or x13,x6,x2

add x14,x2,x2

sw x15,100(x2)

```

Onde estão os hazards de dados?

Considere as instruções a seguir

```

sub x2, x1, x3

and x12, x2, x5

or x13, x6, x2

add x14, x2, x2

sw x15, 100(x2)

```

#### Onde estão os hazards de dados?

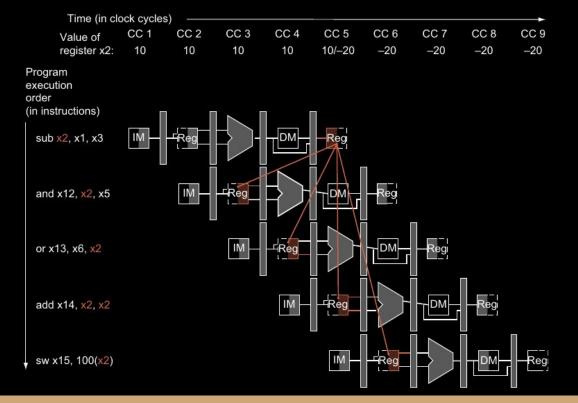

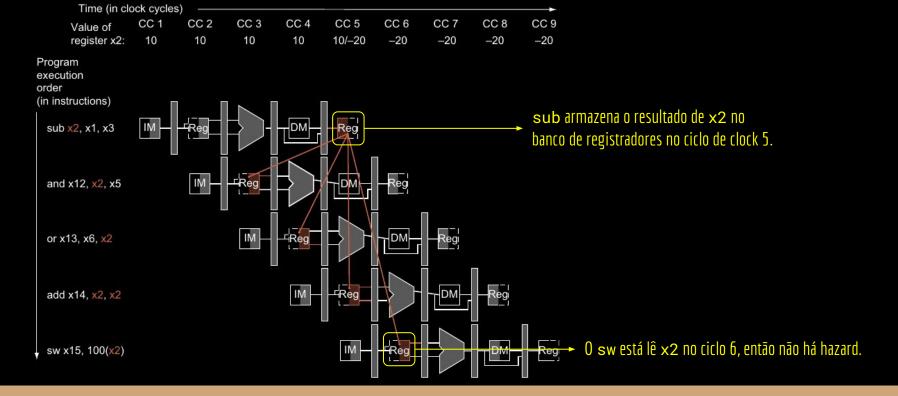

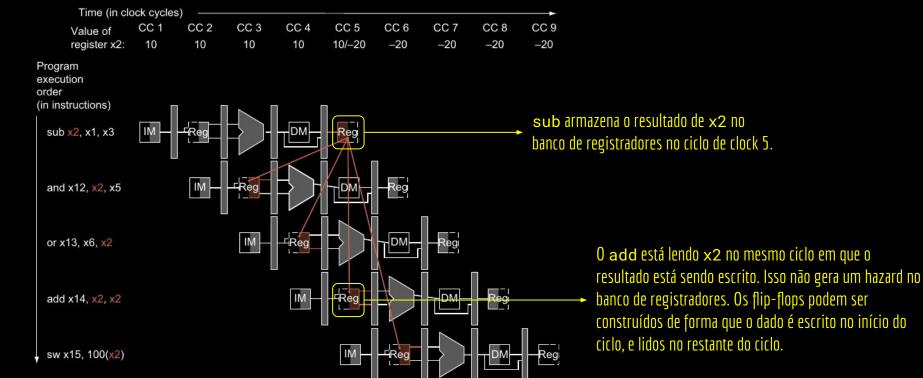

Os trechos marcados dependem do resultado do sub.

Se isso vai causar hazards de dados ou não depende diretamente de como o pipeline é montado, e de sua profundidade.

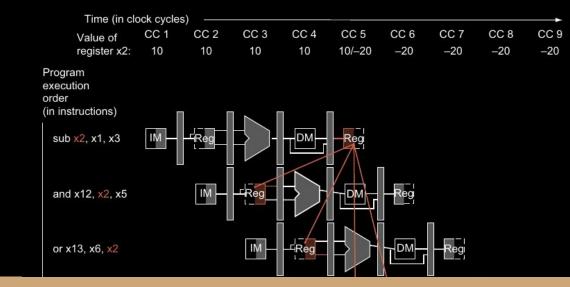

Em que estágio do sub (primeira instrução) o resultado já está pronto e só não foi gravado?

E em que estágio esses valores são realmente utilizados pelas instruções subsequentes (and e or)?

Em que estágio do sub (primeira instrução) o resultado já está pronto e só não foi gravado?

E em que estágio esses valores são realmente utilizados pelas instruções subsequentes (and e or)?

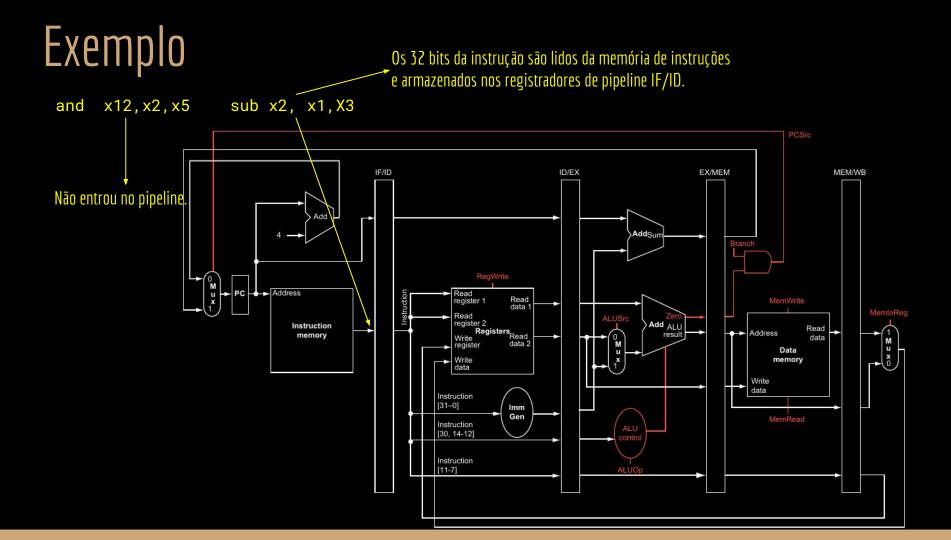

Forward feito "automaticamente" pelo banco de registradores. Considerando o Pipeline do RISC-V Program execution order (in instructions) sub x2, x1, x3 and x12, x2, x5 ⊏Reg or x13, x6, x2 DM add x14, x2, x2 sw x15, 100(x2)

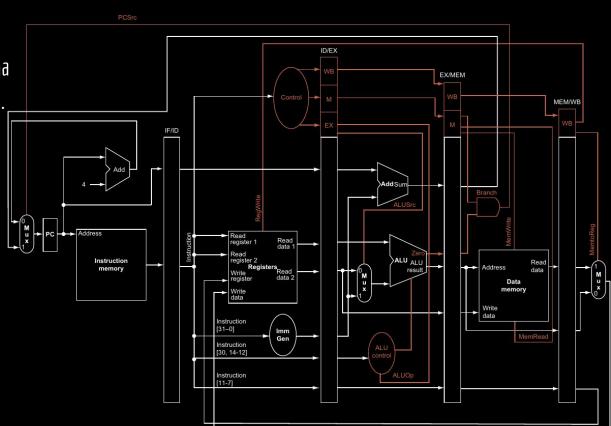

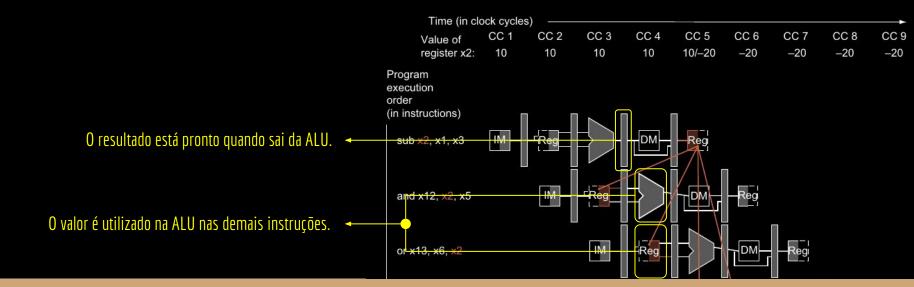

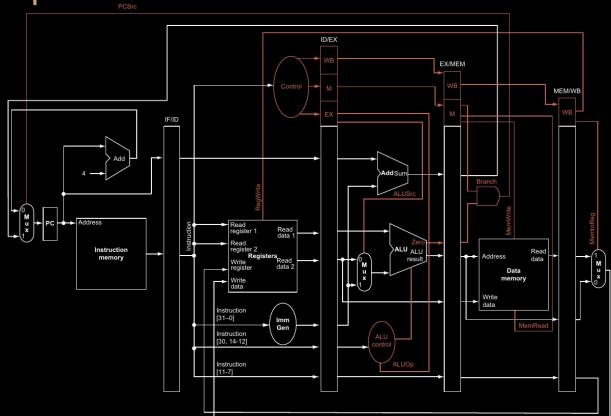

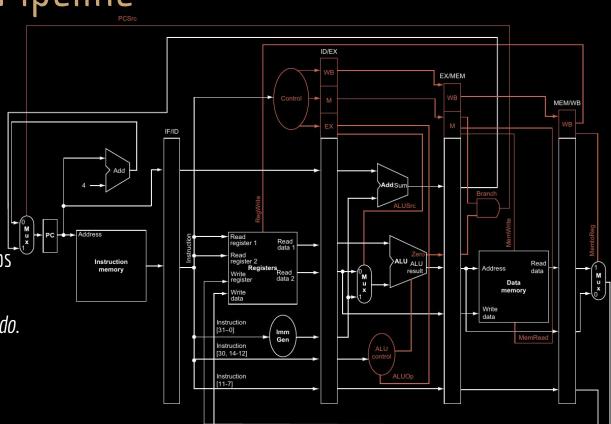

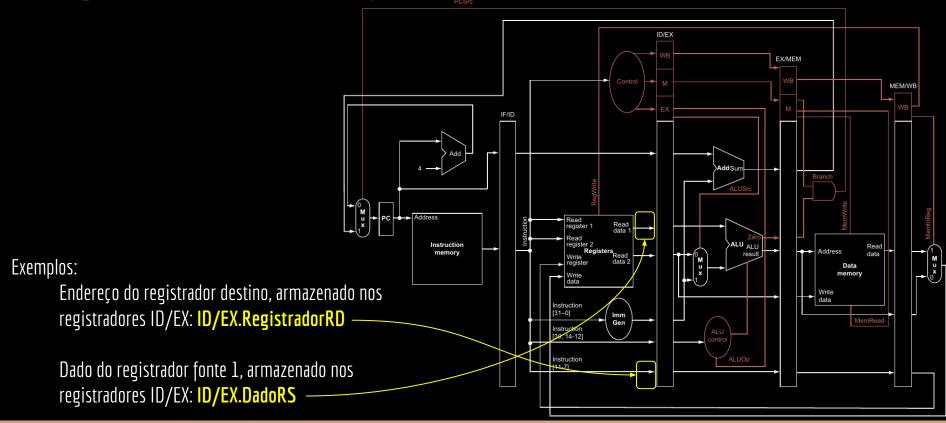

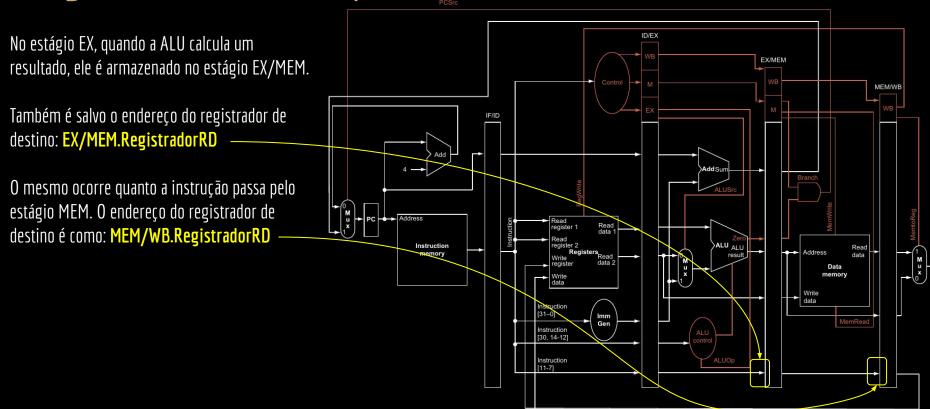

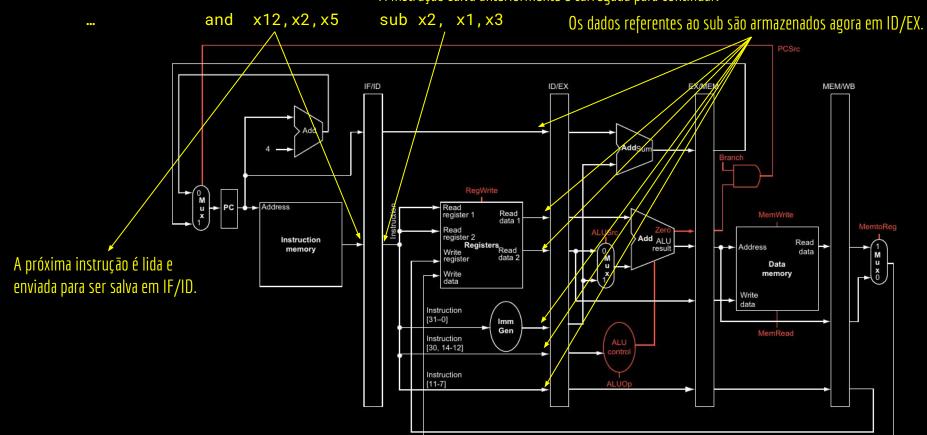

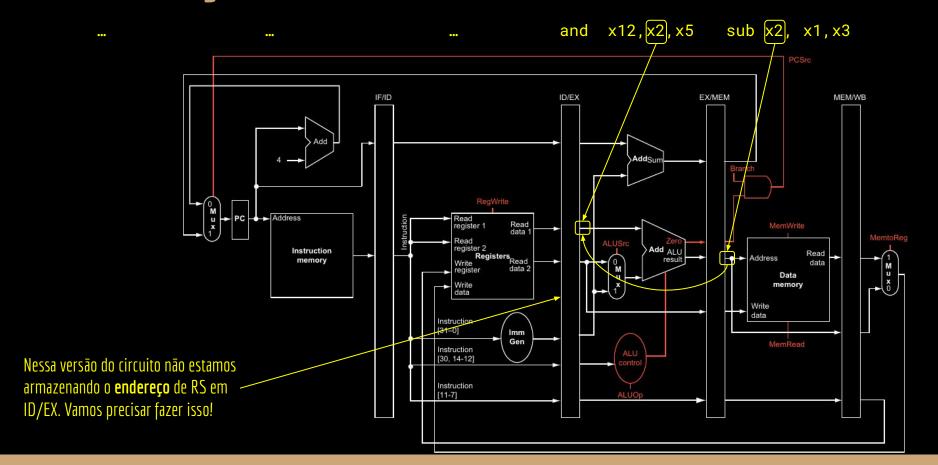

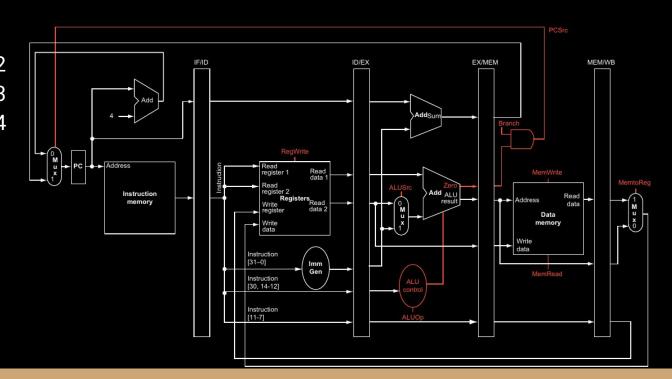

Os registradores de pipeline armazenam as informações relevantes da instrução a cada estágio.

Nomes dos registradores de pipeline: IF/ID, ID/EX, EX/MEM, MEM/WB.

Os registradores de pipeline armazenam as informações relevantes da instrução a cada estágio.

Nomes dos registradores de pipeline: IF/ID, ID/EX, EX/MEM, MEM/WB.

Para referenciar a informação armazenada nos registradores de pipeline, será utilizada a seguinte notação: nomeReqPipeline.nomeDado.

A instrução salva anteriormente é carregada para continuar.

and x12, x2, x5 sub x2, x1, x3 IF/ID ID/EX MEM/WB EX/MEM Add AddSun → PC → Address Read Read data 1 register 1 Read register 2 Add ALU result Instruction Registers Read Read ◆ Address memory data data 2 Data memory Write data Write Instruction [31-0] Imm Gen Instruction [30, 14-12] Instruction [11-7]

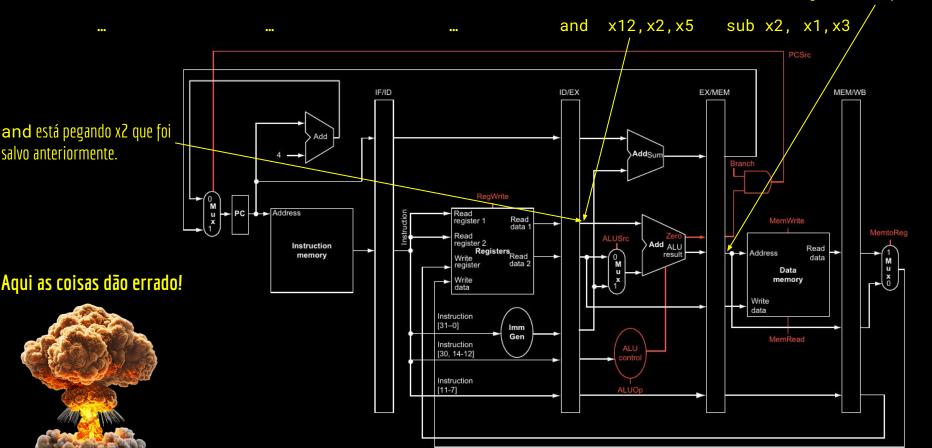

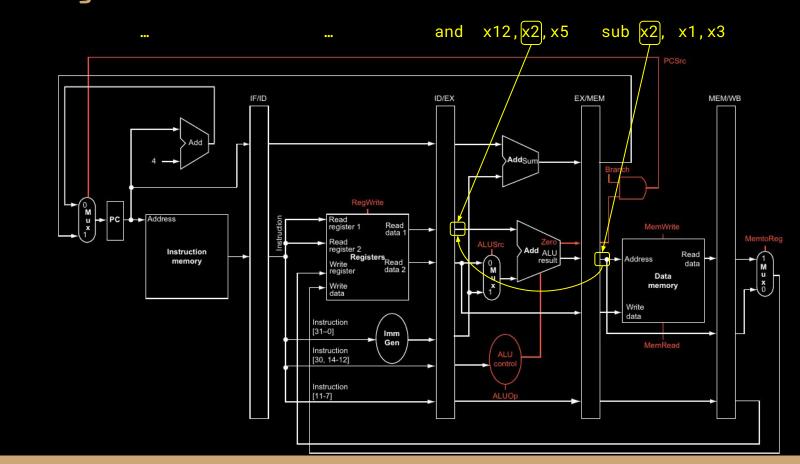

Uma versão mais atual de x2 está presente nos registradores EX/MEM.

### Forwarding

se (ID/EX.RegistradorRS == EX/MEM.RegistradorRD) então

Entrada1ALU = EX.MEM/DadoRD

### Forwarding

#### Hazard de Dados

No exemplo, o 1° fonte da ALU deve vir de EX/MEM.

O mesmo pode acontecer para o 2 fonte.

O resultado pode vir ainda de MEM/WB.

Ainda temos o problema de que não é toda instrução que escreve nos registradores.

O dado em EX/MEM, ou em MEM/WB, mesmo sendo mais recente, **pode não fazer sentido.**

Como saber se o dado nesses estágios vai ser escrito no registrador?

#### Hazard de Dados

No exemplo, o 1° fonte da ALU deve vir de EX/MEM.

O mesmo pode acontecer para o 2 fonte.

O resultado pode vir ainda de MEM/WB.

Ainda temos o problema de que não é toda instrução que escreve nos registradores.

O dado em EX/MEM, ou em MEM/WB, mesmo sendo mais recente, **pode não fazer sentido.**

Uma solução é verificar se o sinal de controle RegWrite está ativo para a instrução que se encontra no estágio EX ou MEM.

Outro problema é se fizermos o forward do registrador \$zero.

Exemplo: addi x0, x1,2

Outro problema é se fizermos o forward do registrador \$zero.

Exemplo: addi x0, x1,2

Podemos tratar esse problema de várias formas.

Exemplo: Especificar que o **montador** gera um erro nesse código Assembly.

Problemas?

Outro problema é se fizermos o forward do registrador \$zero.

Exemplo: addi x0, x1,2

Podemos tratar esse problema de várias formas.

Especificar que o **montador** gera um erro nesse código Assembly.

Funciona, mas...

- E se modificarmos o código de máquina diretamente?

- Quem garante que o montador vai fazer as coisas direito?

- Parece que estamos delegando o problema para quem n\u00e4o deveria ser o respons\u00e1vel.

Outro problema é se fizermos o forward do registrador \$zero.

Exemplo: addi x0, x1,2

Podemos tratar esse problema de várias formas.

Especificar que o **montador** gera um erro nesse código Assembly.

Funciona, mas...

- E se modificarmos o código de máquina diretamente?

- Quem garante que o montador vai fazer as coisas direito?

- Parece que estamos delegando o problema para quem n\u00e4o deveria ser o respons\u00e1vel.

Podemos fazer com que o processador lance uma exceção. Uma boa solução, mas vamos deixar exceções para o futuro.

Ou podemos efetivamente realizar o cálculo e "armazenar" em x0.

O banco de registradores vai ignorar esse resultado e manter x0 com o valor 0.

Simples de fazer. Basta substituir as memórias (ex.: flip-flops) de x0 por um circuito fixo que sempre retorna zero.

Ou podemos efetivamente realizar o cálculo e "armazenar" em x0.

O banco de registradores vai ignorar esse resultado e manter x0 com o valor 0.

Simples de fazer. Basta substituir as memórias (ex.: flip-flops) de x0 por um circuito fixo que sempre retorna zero.

Onde está o problema com os forwardings nesse caso?

Ou podemos efetivamente realizar o cálculo e "armazenar" em x0.

O banco de registradores vai ignorar esse resultado e manter x0 com o valor 0.

Simples de fazer. Basta substituir as memórias (ex.: flip-flops) de x0 por um circuito fixo que sempre retorna zero.

#### Onde está o problema com os forwardings nesse caso?

```

addi x0, x1, 2

```

addi x2, x0, 15 #se fizermos os forward do x0, será usado um valor que será descartado!

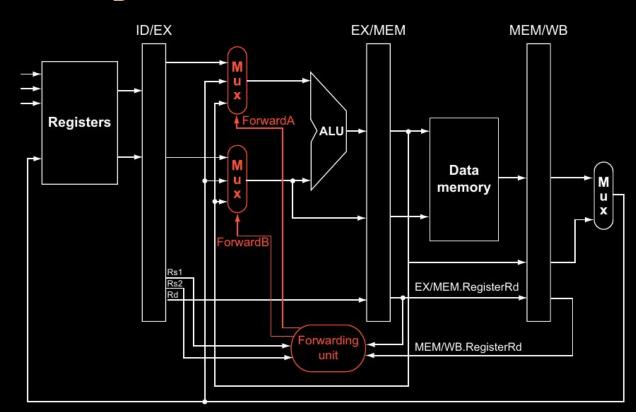

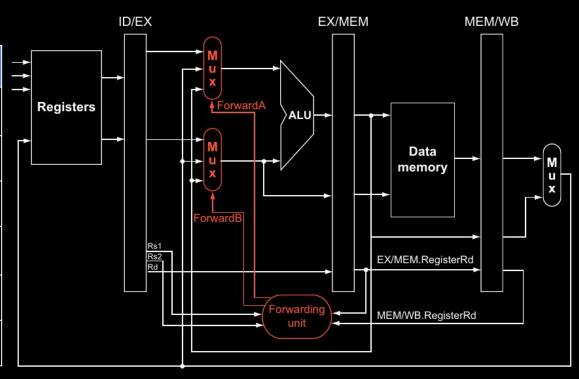

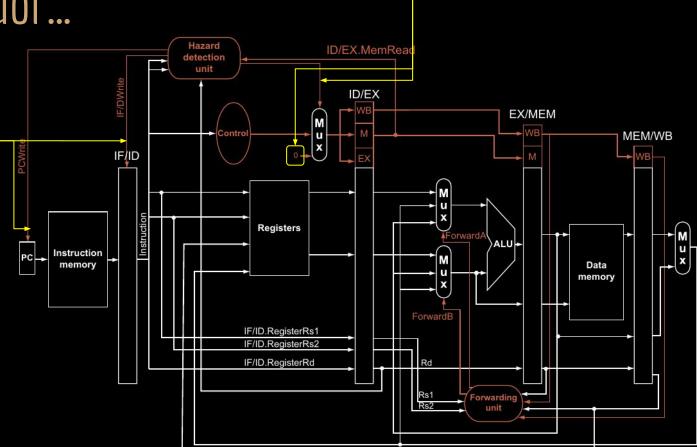

# Unidade de Forwarding

Para simplificar, essa versão do circuito não está com o multiplexador para escolher entre o registrador e o campo imediato como segundo operando da ALU.

**Faça você mesmo:** Adicione esse multiplexador e compare com a solução do livro.

# Unidade de Forwarding

| Sinal MUX     | Fonte  | Descrição                                                                |

|---------------|--------|--------------------------------------------------------------------------|

| ForwardA = 00 | ID/EX  | Primeiro operando da ALU vem do<br>banco de registradores (sem forward). |

| ForwardA = 10 | EX/MEM | Primeiro operando da ALU vem de<br>EX/MEM (forward).                     |

| ForwardA = 01 | MEM/WB | Primeiro operando da ALU vem de<br>MEM/WB (forward).                     |

| ForwardB = 00 | ID/EX  | Primeiro operando da ALU vem do<br>banco de registradores (sem forward). |

| ForwardB = 10 | EX/MEM | Primeiro operando da ALU vem de<br>EX/MEM (forward).                     |

| ForwardB = 01 | MEM/WB | Primeiro operando da ALU vem de<br>MEM/WB (forward).                     |

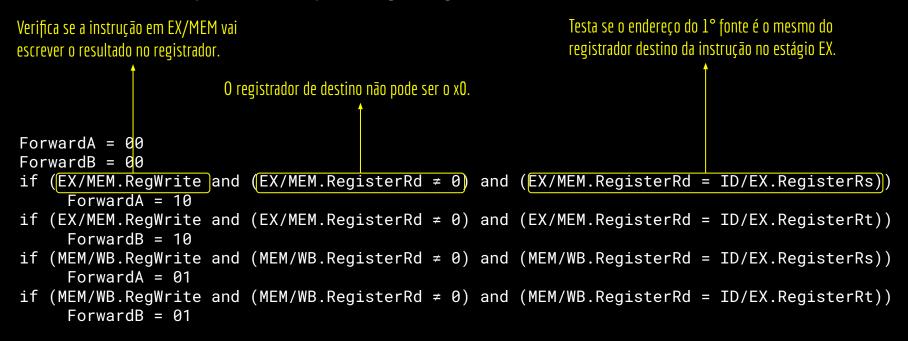

# Condições

As condições testadas pela unidade de forwarding são algo como:

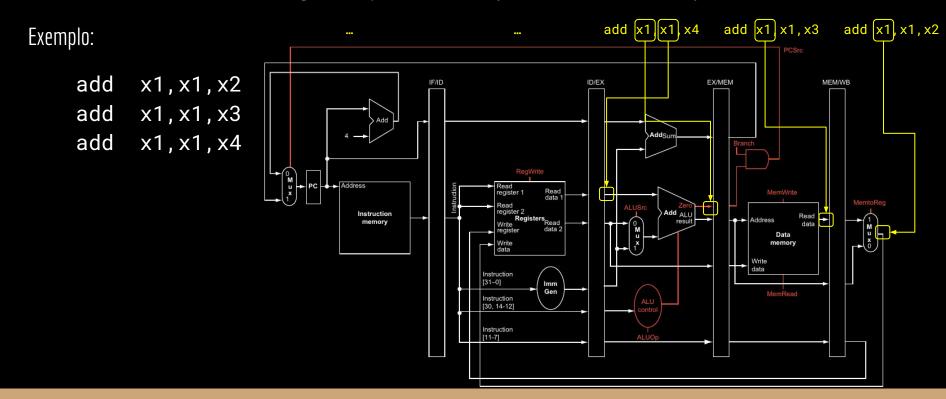

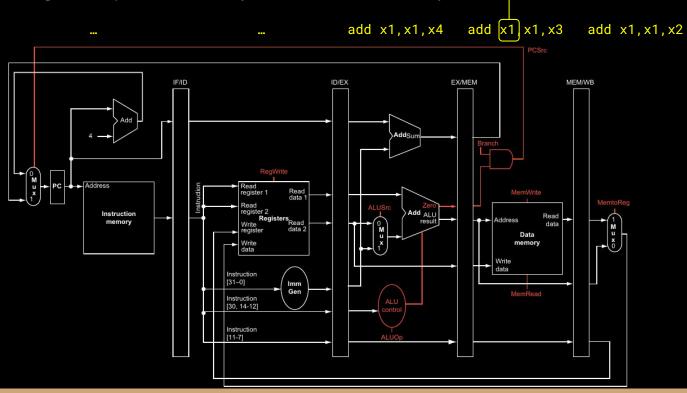

### Mais Problemas

O resultado ainda não salvo de um registrador pode estar em EX/MEM, e também em MEM/WB.

#### Exemplo:

add x1,x1,x2 add x1,x1,x3 add x1,x1,x4

### Mais Problemas

O resultado ainda não salvo de um registrador pode estar em EX/MEM, e também em MEM/WB.

### Mais Problemas

Resultado mais recente.

O resultado ainda não salvo de um registrador pode estar em EX/MEM, e também em MEM/WB.

add x1,x1,x2 add x1,x1,x3 add x1,x1,x4

## Condições Atualizadas

```

ForwardA = 00

ForwardB = 00

if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRs))

ForwardA = 10

if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd = ID/EX.RegisterRt))

ForwardB = 10

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and not(EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd ≠ ID/EX.RegisterRs))

and (MEM/WB.RegisterRd = ID/EX.RegisterRs))

ForwardA = 01

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and not(EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0) and (EX/MEM.RegisterRd ≠ ID/EX.RegisterRt))

and (MEM/WB.RegisterRd = ID/EX.RegisterRt))

ForwardB = 01

```

## Unidade de forwarding

A unidade desenvolvida serve para o estágio EX.

Hazards de dados ainda podem acontecer no estágio MEM.

Exemplo: um **1**w seguido de um **s**w se referenciando ao mesmo endereço de memória.

A unidade de forwarding em MEM é mais simples do que a em EX.

**Exercício:** defina essa unidade.

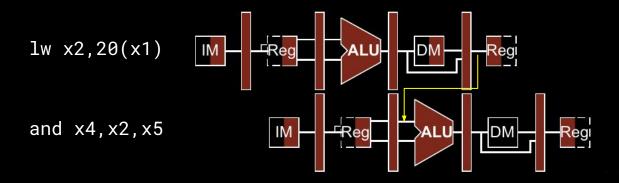

Não é possível solucionar qualquer hazard de dados através de forwardings.

#### Exemplo:

Não é possível solucionar qualquer hazard de dados através de forwardings.

Precisamos de um pipeline stall.

Inserir **bolhas** no pipeline.

Uma bolha é inserida efetivamente com uma instrução que não executa operação alguma.

Esse tipo de instrução geralmente é chamada de **nop** – no operation.

Não escreve nos registradores.

PC não é atualizado (depende se o nop foi injetado pelo programador ou pelo hardware).

Não escreve na memória.

Não altera as informações nos registradores de pipeline.

Nosso processador e pipeline são simples.

A única combinação que causa stalls são loads seguidos de alguma instrução que usa o conteúdo do registrador carregado.

#### Exemplo:

```

lw $s1, 4($s2)

add $s4, $s1,$s5

```

O stall é de uma instrução.

Não precisamos adicionar mais de um **nop** (bolha) no meio das instruções.

O controle da unidade de detecção de hazards pode ser:

```

if (ID/EX.MemRead and ((ID/EX.RegisterRt = IF/ID.RegisterRs) or (ID/EX.RegisterRt = IF/ID.RegisterRt)))

pipeline stall

```

Envia o código O para todos os sinais de controle.

No processador...

Bits de enable para desabilitar a escrita.

# Pipeline não é fácil!

Criar o pipeline e tratar os seus hazards não é fácil, mesmo em uma CPU simples.

Imagina tratar disso em um Pentium 4 Prescott!

| Microprocessador     | Ano  | Clock     | Estágios<br>Pipeline | Tamanho<br>Despacho | Fora de ordem? | CPUs por<br>Chip | Potência |

|----------------------|------|-----------|----------------------|---------------------|----------------|------------------|----------|

| 486                  | 1989 | 0,025 GHz | 5                    | 1                   | Nāo            | 1                | 5 W      |

| Pentium              | 1993 | 0,066 GHz | 5                    | 2                   | Nāo            | 1                | 10 W     |

| Pentium Pro          | 1997 | 0,2 GHz   | 10                   | 3                   | Sim            | 1                | 29 W     |

| Pentium 4 Willamette | 2001 | 2 GHz     | 22                   | 3                   | Sim            | 1                | 75 W     |

| Pentium 4 Prescott   | 2004 | 3,6 GHz   | 31                   | 3                   | Sim            | 1                | 103 W    |

| Intel Core           | 2006 | 3 GHz     | 14                   | 4                   | Sim            | 2                | 75 W     |

| Core i7 Nehalem      | 2008 | 3,6 GHz   | 14                   | 4                   | Sim            | 2-4              | 87 W     |

| Core Westmere        | 2010 | 3,73 GHz  | 14                   | 4                   | Sim            | 6                | 130 W    |

| Core i7 Ivy Bridge   | 2012 | 3,4 GHz   | 14                   | 4                   | Sim            | 6                | 130 W    |

| Core Broadwell       | 2014 | 3,7 GHz   | 14                   | 4                   | Sim            | 10               | 140 W    |

| Core i9 Skylake      | 2016 | 3,1 GHz   | 14                   | 4                   | Sim            | 14               | 165 W    |

| Intel Ice Lake       | 2018 | 4,2 GHz   | 14                   | 4                   | Sim            | 16               | 185 W    |

| Intel Raptor Cove    | 2022 | 6.2 GHz   | 12                   | -                   | Sim            | 24               | -        |

| Intel Lion Cove      | 2024 | _         | 10                   | _                   | Sim            | _                | _        |

## Pipeline nāo é fácil!

Criar o pipeline e tratar os seus hazards não é fácil, mesmo em uma CPU simples.

Imagina tratar disso em um Pentium 4 Prescott!

Obs.: é o pipeline do Pentium 4 que vai cair no

exame.

| Microprocessador     | Ano  | Clock     | Estágios<br>Pipeline | Tamanho<br>Despacho | Fora de ordem? | CPUs por<br>Chip | Potência |

|----------------------|------|-----------|----------------------|---------------------|----------------|------------------|----------|

| 486                  | 1989 | 0,025 GHz | 5                    | 1                   | Nāo            | 1                | 5 W      |

| Pentium              | 1993 | 0,066 GHz | 5                    | 2                   | Nāo            | 1                | 10 W     |

| Pentium Pro          | 1997 | 0,2 GHz   | 10                   | 3                   | Sim            | 1                | 29 W     |

| Pentium 4 Willamette | 2001 | 2 GHz     | 22                   | 3                   | Sim            | 1                | 75 W     |

| Pentium 4 Prescott   | 2004 | 3,6 GHz   | 31                   | 3                   | Sim            | 1                | 103 W    |

| Intel Core           | 2006 | 3 GHz     | 14                   | 4                   | Sim            | 2                | 75 W     |

| Core i7 Nehalem      | 2008 | 3,6 GHz   | 14                   | 4                   | Sim            | 2-4              | 87 W     |

| Core Westmere        | 2010 | 3,73 GHz  | 14                   | 4                   | Sim            | 6                | 130 W    |

| Core i7 Ivy Bridge   | 2012 | 3,4 GHz   | 14                   | 4                   | Sim            | 6                | 130 W    |

| Core Broadwell       | 2014 | 3,7 GHz   | 14                   | 4                   | Sim            | 10               | 140 W    |

| Core i9 Skylake      | 2016 | 3,1 GHz   | 14                   | 4                   | Sim            | 14               | 165 W    |

| Intel Ice Lake       | 2018 | 4,2 GHz   | 14                   | 4                   | Sim            | 16               | 185 W    |

| Intel Raptor Cove    | 2022 | 6.2 GHz   | 12                   | -                   | Sim            | 24               | -        |

| Intel Lion Cove      | 2024 | -         | 10                   | -                   | Sim            | -                | -        |

#### Exercícios

- Releia os slides, discutindo cada ponto de forma detalhada com os colegas.

- 2. Volte nas aulas anteriores e verifique que ao enviar zero em todos os sinais de controle, nada será alterado ao final de uma instrução.

- 3. Usando os slides como exemplo, crie uma unidade de forwarding para o estágio MEM do pipeline.

## Referências

Patterson, Hennessy.

Computer Organization and

Design RISC-V Edition: The

Hardware Software

Interface. 2020.

Patterson, Hennessy. Computer Organization and Design MIPS Edition: The Hardware/Software Interface. 2020.

Stallings, W. Organização de Arquitetura de Computadores. 10a Ed. 2016.

Hennessy, Patterson. Arquitetura de Computadores: uma abordagem quantitativa. 2019.

## Licença

Esta obra está licenciada com uma Licença Creative Commons Atribuição 4.0 Internacional.